-

TOPSwitchGaN doubles flyback output to 440 W, achieving high efficiency and performance without resonant and LLC topologies. Learn More

-

Language

- Login / Register

|

Product

|

Product

|

Data Sheet

|

Output Power (Max) - Enclosed, 230V

|

Output Power (Max) - Open Frame, 230V

|

Output Power (Max) - Enclosed, Univ

|

Output Power (Max) - Open Frame, Univ

|

IC Package

|

Control Features

|

Protection Features

|

Over-Temperature Response

|

Secondary Response

|

Voltage - Input (Min)

|

Voltage - Input (Max)

|

Control Scheme

|

Mounting Type

|

Product Type

|

Breakdown Voltage

|

Temperature - Operating (Max)

|

Temperature - Operating (Min)

|

Internal Switch

|

Auto-Restart & Overvoltage Response

|

Cable Drop Compensation

|

Topology

|

Output Profile

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Data Sheet

View Data Sheet

|

Output Power (Max) - Enclosed, 230V

3.0 W

|

Output Power (Max) - Open Frame, 230V

3.0 W

|

Output Power (Max) - Enclosed, Univ

3.0 W

|

Output Power (Max) - Open Frame, Univ

3.0 W

|

IC Package

SO-8C

|

Control Features

Cable Drop Compensation, Frequency Jittering, Auto-Restart/Latching Fault Response, On/Off Control

|

Protection Features

Output Undervoltage, Overtemperature, Input Overvoltage, Input Undervoltage, Output Overvoltage, Output Short Circuit, Output Open Loop

|

Over-Temperature Response

Hysteretic

|

Secondary Response

Auto-restart

|

Voltage - Input (Min)

85 V

|

Voltage - Input (Max)

265 V

|

Control Scheme

Primary-side

|

Mounting Type

Surface Mount

|

Product Type

IC

|

Breakdown Voltage

700 V

|

Temperature - Operating (Max)

150 °C

|

Temperature - Operating (Min)

-40 °C

|

Internal Switch

Yes

|

Auto-Restart & Overvoltage Response

Latch Off

|

Cable Drop Compensation

X

|

Topology

Flyback

|

Output Profile

CV/CC

|

||

|

Data Sheet

View Data Sheet

|

Output Power (Max) - Enclosed, 230V

6.0 W

|

Output Power (Max) - Open Frame, 230V

9.0 W

|

Output Power (Max) - Enclosed, Univ

5.0 W

|

Output Power (Max) - Open Frame, Univ

8.0 W

|

IC Package

SO-8C

|

Control Features

Cable Drop Compensation, Frequency Jittering, Auto-Restart/Latching Fault Response, On/Off Control

|

Protection Features

Output Undervoltage, Overtemperature, Input Overvoltage, Input Undervoltage, Output Overvoltage, Output Short Circuit, Output Open Loop

|

Over-Temperature Response

Hysteretic

|

Secondary Response

Auto-restart

|

Voltage - Input (Min)

85 V

|

Voltage - Input (Max)

265 V

|

Control Scheme

Primary-side

|

Mounting Type

Surface Mount

|

Product Type

IC

|

Breakdown Voltage

700 V

|

Temperature - Operating (Max)

150 °C

|

Temperature - Operating (Min)

-40 °C

|

Internal Switch

Yes

|

Auto-Restart & Overvoltage Response

Latch Off

|

Cable Drop Compensation

X

|

Topology

Flyback

|

Output Profile

CV/CC

|

Product Details

Description

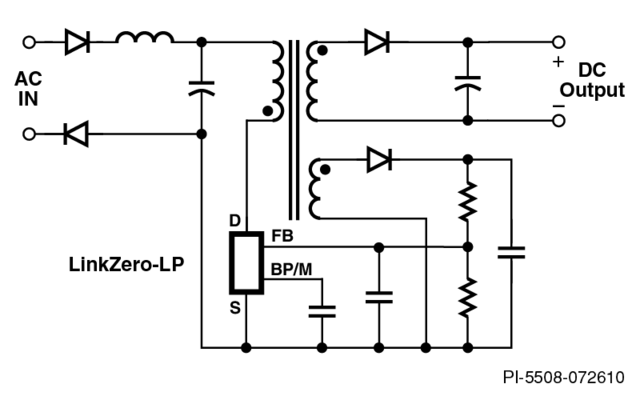

LinkZero-LP, an upgrade to PI's popular LinkSwitch-LP, incorporates new technology which enables the device to automatically enter into and wake up from no-load mode while disipating less than 5 mW - substantially less than the IEC definition of zero no-load power consumption. The tightly specified FEEDBACK pin voltage reference enables universal input primary side regulated power supplies with accurate constant voltage from 5% to full load. Start-up and operating power are derived directly from the DRAIN pin which eliminates start-up circuitry. The internal oscillator frequency is jittered to significantly reduce both quasi-peak and average EMI, minimizing filter cost.

Product Highlights

Lowest System Cost with Zero No-Load

- Automatically enters zero input power mode when load is disconnected

- Simple upgrade to existing LinkSwitch-LP designs

- Very tight IC parameter tolerances improve system manufacturing yield

- Suitable for low-cost clampless designs

- Frequency jittering greatly reduces EMI filter cost

- Extended package creepage improves system field reliability

Advanced Protection/Safety Features

- Accurate hysteretic thermal shutdown protection – automatic recovery reduces field returns

- Universal input range allows worldwide operation

- Auto-restart reduces delivered power by >85% during short-circuit and open loop fault conditions

- Simple ON/OFF control, no loop compensation needed

- High bandwidth provides excellent transient load response with no overshoot

EcoSmart – Energy Efficient

- No-load consumption as low as 4 mW at 230 VAC input*

- Easily meets all global energy efficiency regulations with no added components

- ON/OFF control provides constant efficiency to very light loads

Applications

- Chargers for cell/cordless phones, PDAs, power tools, MP3/portable audio devices, shavers, etc.

* IEC 62301 Clause 4.5 rounds standby power use below 5 mW to zero.

Resources

Data Sheets

Design Tools

Product Flyers

© 2026 Power Integrations. All Rights Reserved