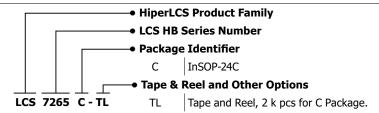

# **HiperLCS-2** Chipset

Off-Line LLC Switcher ICs with Integrated 600 V Half-Bridge Synchronous Rectification and FluxLink Feedback

### **Product Highlights**

### **Highly Integrated, Compact Footprint**

- Up to 98.1% efficiency

- Very low component count and small footprint package

- Up to 1650 W with heat sink

- · Self-powered start-up

- 600 V Half-Bridge, rugged fast recovery body diode, auto dead time, hard switch detect, current sense and thermal detect

- · HB auto dead time and hard switch detect

- Selectable center frequency (90, 120, 180, 240 kHz)

- Secondary-side sensing and feedback control with fast transient response

- · Synchronous rectification driver

- Integrated FluxLink™, HIPOT-isolated control link

### EcoSmart™ - Energy Efficient

- As low as 65 mW no-load including line sense

- Output always in regulation, 0-100% load step

- Easily meets all global energy efficiency regulations

### **Advanced Protection / Safety Features**

- HB and SR shoot-through protection

- Power-up pin open/short check

- System short-circuits, thermal, HB OCP, FB open, fast input line UV/OV and PMAX protection

### **Scalable Power Delivery**

- 80 W 1440 W for adapter (free convection)

- 520 W 1650 W open frame (forced air)

### **Optional Features**

- Auto-restart or latching fault response for output OVP/UVP

- Latching or hysteretic primary over-temperature protection

- · External faults detect and remote on/off

- Inrush-relay drive output pin

- Provides start-up bias for PFC stage

### **Full Safety and Regulatory Compliance**

- Reinforced isolation, isolation voltage >4000 VAC

- UL1577 isolation voltage 4000 VAC (max), CQC and TUV (EN62368-1) safety approved

### **Applications**

- High efficiency power supplies up to 1650 W continuous

- Consumer electronics TV, PC, e-bike, EV 2-/3-wheeler and tool chargers

### **Description**

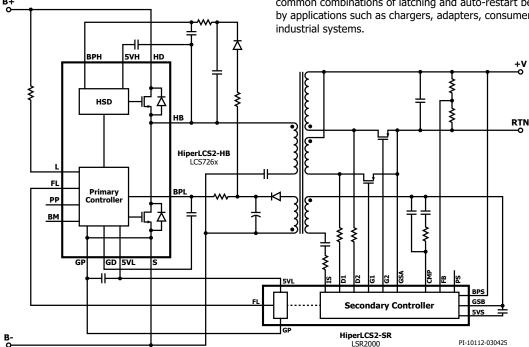

The HiperLCS™-2 chipset achieves high efficiency and compact size in power supplies up to 220 W with no heat sink and 1650 W with heat sink. This IC chipset simplifies the design and manufacture of LLC resonant power converters. The LCS726x primary-side devices incorporate 600 V FREDFET in a half-bridge arrangement with control, level shifting, drive and self-powered start-up. The LSR2000C master controller device provides reinforced isolated feedback, output sensing and SR management.

HiperLCS-2 chipset incorporates multiple protection features including line over and undervoltage protection, output overvoltage and over-temperature shutdown. Device fault response options support common combinations of latching and auto-restart behaviors required by applications such as chargers, adapters, consumer electronics and industrial systems.

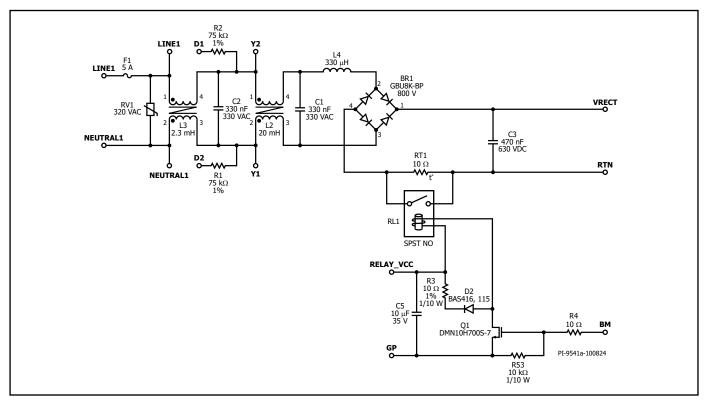

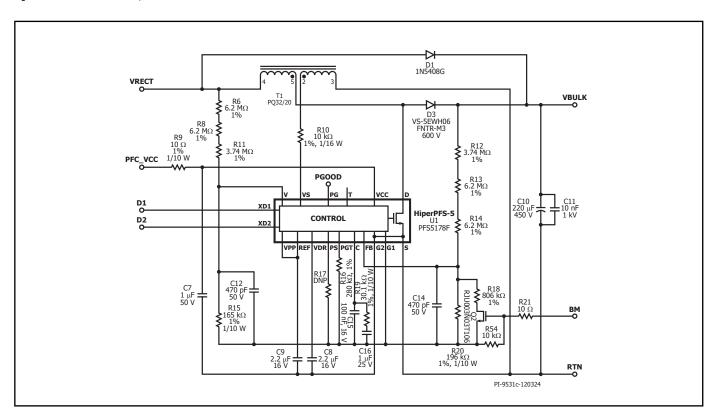

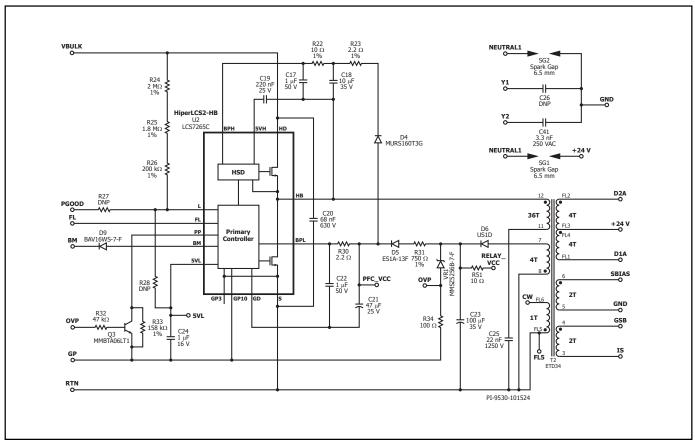

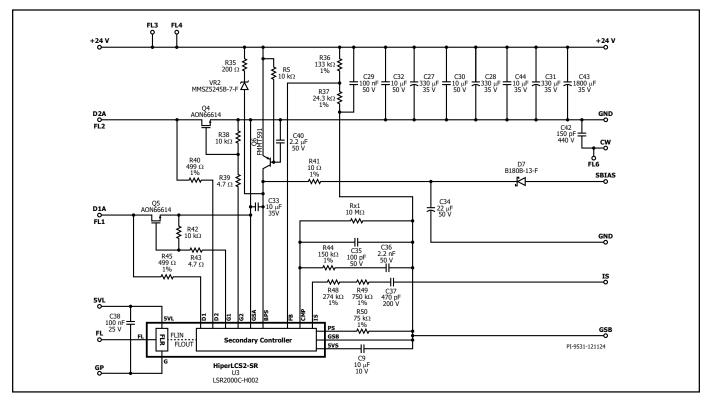

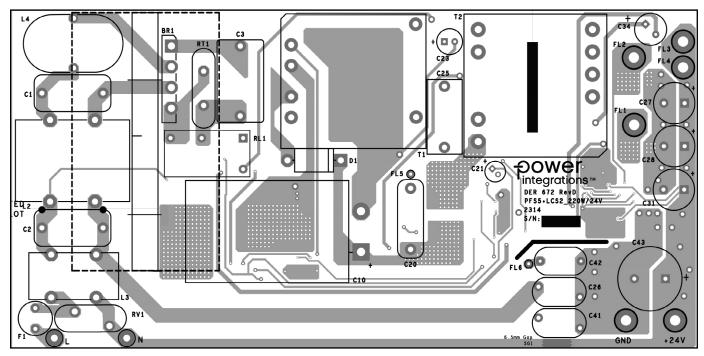

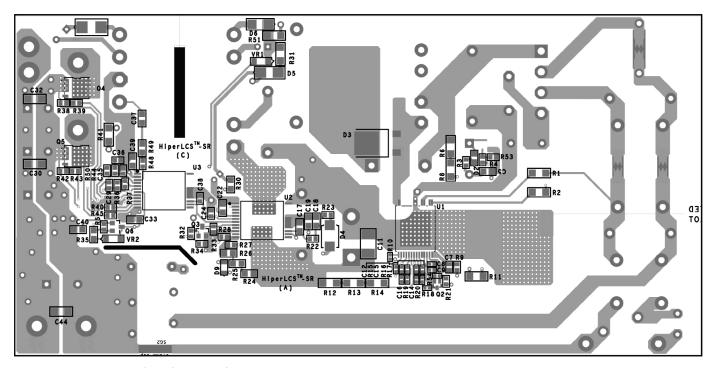

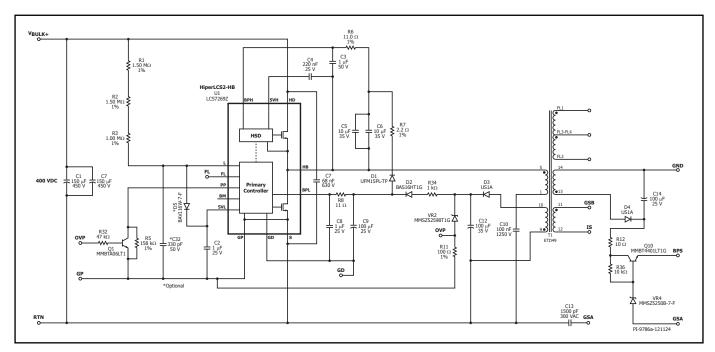

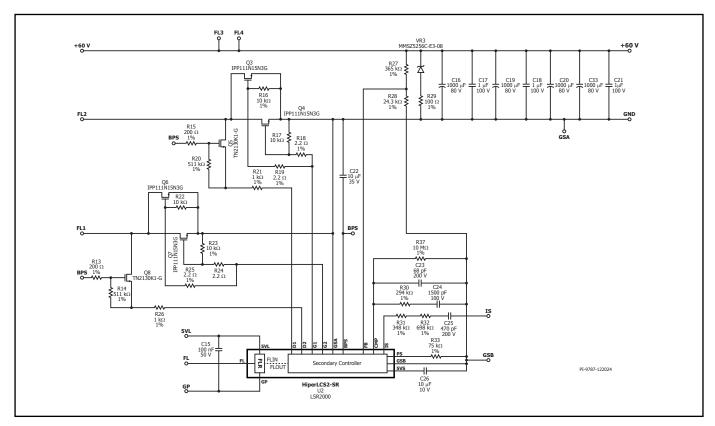

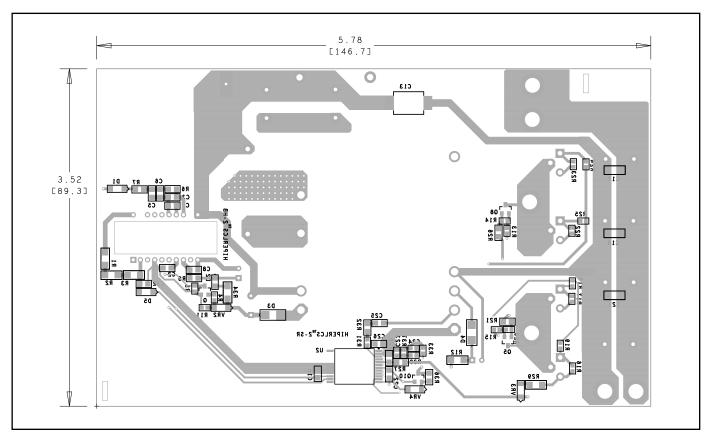

Figure 1. Typical Application Schematic.

| Output | <b>Power</b> | <b>Table</b> |

|--------|--------------|--------------|

|--------|--------------|--------------|

| Power    | Safety              | 385 VDC ±5%          |                                   |                         |  |  |  |

|----------|---------------------|----------------------|-----------------------------------|-------------------------|--|--|--|

| Device   | Isolation<br>Device | Adapter <sup>1</sup> | Forced Air<br>Cooled <sup>2</sup> | Peak Power <sup>3</sup> |  |  |  |

| LCS7260C |                     | 80 W                 | N/A                               | 135 W                   |  |  |  |

| LCS7262C | - LSR2000C          | 120 W                | N/A                               | 205 W                   |  |  |  |

| LCS7265C |                     | 220 W                | N/A                               | 375 W                   |  |  |  |

| LCS7265Z |                     | 460 W                | 520 W                             | 780 W                   |  |  |  |

| LCS7268Z |                     | 720 W                | 830 W                             | 1225 W                  |  |  |  |

| LCS7269Z |                     | 1440 W               | 1650 W                            | 2450 W                  |  |  |  |

Table 1. Output Power Table. Notes:

- 1. Power Device: Minimum continuous power in a typical non-ventilated enclosed typical size adapter measured at 40 °C ambient. Max output power is dependent on the design, with condition that  $\rm T_{\rm J}$  <110 °C.

- 2. Forced air cooled: With combination of heat sink and airflow, sufficient to maintain  $T_1 < 110$  °C

- 3. Power Device: Minimum peak power capability (not thermally limited).

Where Duty (Pk) = P(pk 50 ms) / P(adapter) < = 170%.

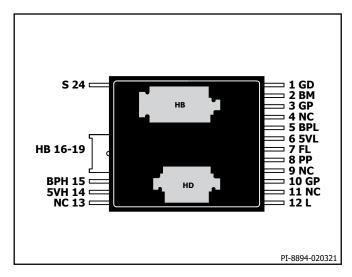

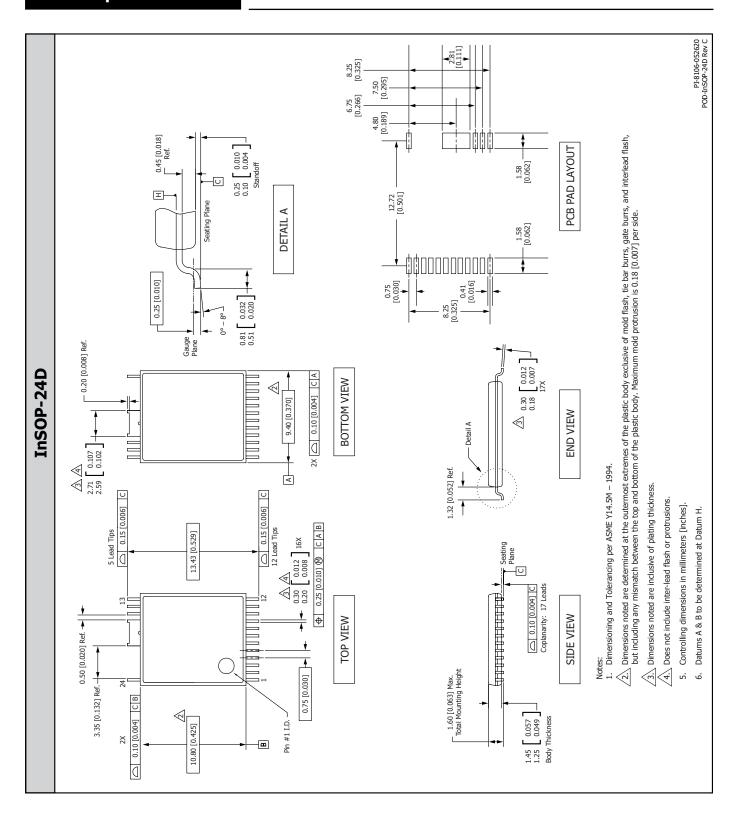

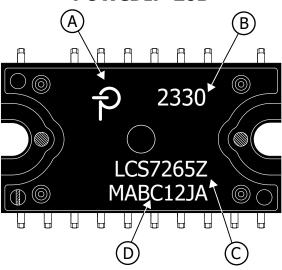

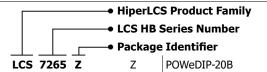

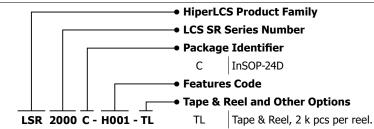

Figure 2. Primary-Side Packages. (Left) POWeDIP-20B (Right) InSOP-24C Top View.

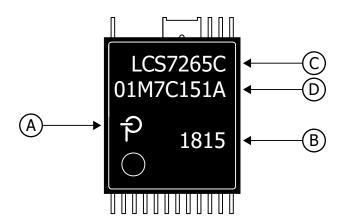

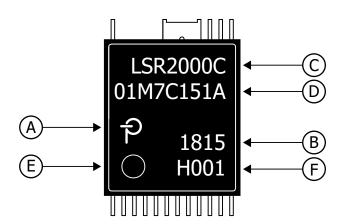

Figure 3. HiperLCS2-SR. Safety Isolation Package, InSOP-24D Top View.

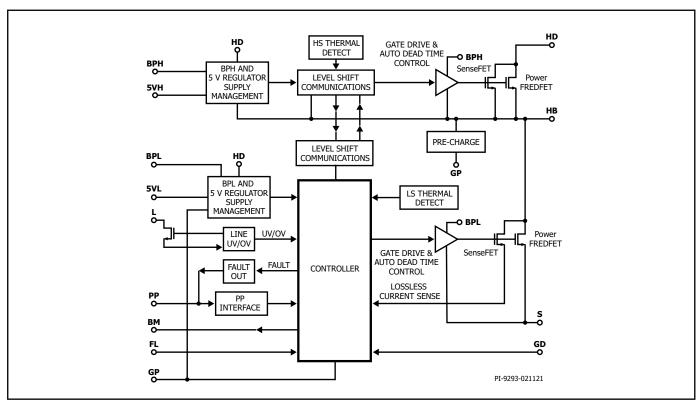

Figure 4. Primary Controller (Low-Side and High-Side), Block Diagram.

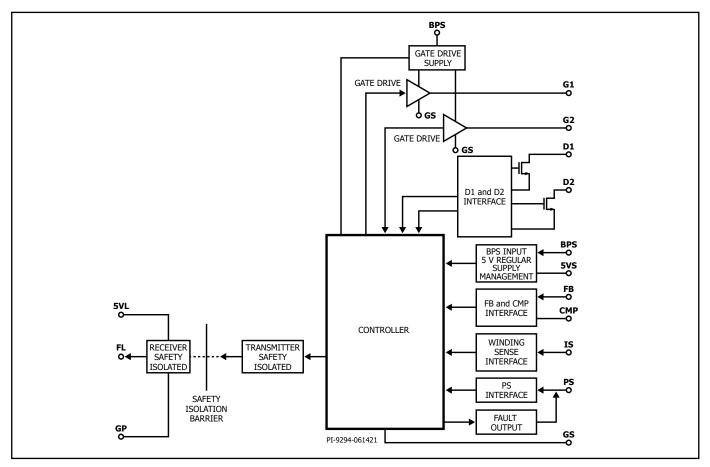

Figure 5. Safety Isolation and Secondary Controller Block Diagram.

# Pin Functional Description – Primary-Side Device LCS726xC

### Low-Side

### PRIMARY GROUND (GD) (Pin 1)

Primary gate-drive ground. Should be capacitively decoupled to primary supply pin (BPL).

### **BURST MODE (BM) (Pin 2)**

Small signal output indicating deep burst mode operation. Can be coupled to control external primary-side circuits.

### PRIMARY GROUND (GP) (Pin 3)

Small signal primary ground. Should be capacitively decoupled to primary 5 V (5VL) pin.

### NO CONNECTION (NC) (Pin 4)

Pin not connected. Leave open.

### **BYPASS LOW-SIDE (BPL) (Pin 5)**

Power supply pin for primary low-side device. Should be capacitively decoupled to primary gate-drive ground (GD) pin.

### PRIMARY LOW-SIDE 5 V (5VL) (Pin 6)

Primary low-side small signal 5 V IC-supply pin. Also provides bias power to the Primary-side of the Isolation device (LSR2000). 5VL should be capacitively decoupled to primary small signal ground (GP).

### FLUXLINK INPUT (FL) (Pin 7)

Small signal input for FLUX LINK signal.

### PROGRAM PRIMARY (PP) (Pin 8)

Small signal connection for customer configuration selection components. Also used in some configurations as small signal current input to receive power-good (remote on/off), signal to command device activation. Likewise used in some configurations as small signal current input for external fault. This pin also outputs logic level error code during fault conditions.

### NO CONNECT (NC) (Pin 9)

Pin not connected. Leave open.

### PRIMARY GROUND (GP) (Pin 10)

Small signal primary ground. Should be capacitively decoupled to primary 5 V (5VL) pin.

### NO CONNECT (NC) (Pin 11)

Pin not connected. Leave open.

### LINE SENSE (L) (Pin 12)

High-voltage small signal current input pin. Used to detect line-input voltage. Also used in some configurations as small signal input to receive power-good (remote on/off) signal to command device activation.

Figure 6. HiperLCS2 Primary-Side LCS726XC, InSOP-24C (Bottom View.)

### **High-Side**

### NO CONNECT (NC) (Pin 13)

Pin not connected. Leave open.

### HIGH-SIDE 5 V (5VH) (Pin 14)

Primary high-side small signal 5 V IC-supply pin. Should be capacitively decoupled to half-bridge (HB). NOTE: this pin floats on the half-bridge switching voltage, can be at high-voltage with respect to primary grounds.

### **BYPASS HIGH-SIDE (BPH) (Pin 15)**

Power supply for primary high-side device. Should be capacitively decoupled to half-bridge (HB) pin. NOTE: this pin floats on the half-bridge switching voltage, can be at high-voltage with respect to primary grounds.

### HALF-BRIDGE (HB) (Pins 16-19 and Back Side HB Pad)

High-voltage and high current connection point for low-side MOSFET DRAIN and high-side MOSFET SOURCE. The half-bridge node typically switches between primary ground and primary input bus (HD).

### SOURCE (S) (Pin 24)

High current Power ground return for half-bridge switch current. Also, at same potential as other small-signal primary grounds.

### **HD (Pin Back-Side Solder Pad)**

High current, high-side MOSFET Drain and connection to system high-voltage input bus.

Figure 7. Primary-Side Packages. (Right Upper), InSOP-24C Top View (Right Lower), InSOP-24C Bottom View

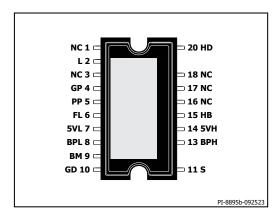

# Pin Functional Description – Primary-Side Device LCS726xZ

#### Low-Side

### NO CONNECT (NC) (Pin 1)

Pin not connected. Leave open.

### LINE SENSE (L) (Pin 2)

High-voltage small signal current input pin. Used to detect line-input voltage. Also used in some configurations as small signal input to receive power-good (remote on/off) signal to command device activation.

### NO CONNECT (NC) (Pin 3)

Pin not connected. Leave open.

### PRIMARY GROUND (GP) (Pin 4)

Small signal primary ground. Should be capacitively decoupled to primary 5 V (5VL) pin.

### PROGRAM PRIMARY (PP) (Pin 5)

Small signal connection for customer configuration selection components. Also used in some configurations as small signal current input to receive power-good (remote on/off), signal to command device activation. Likewise used in some configurations as small signal current input for external fault. This pin also outputs logic level error code during faults.

### FLUXLINK INPUT (FL) (Pin 6)

Small signal input for FLUX LINK signal.

### PRIMARY LOW-SIDE 5 V (5VL) (Pin 7)

Primary low-side small signal 5 V IC-supply pin. Also provides bias power to the Primary-side of the Isolation device (LSR2000). 5VL should be capacitively decoupled to primary small signal ground (GP).

### **BYPASS LOW-SIDE (BPL) (Pin 8)**

Power supply pin for primary low-side device. Should be capacitively decoupled to primary gate-drive ground (GD).

### **BURST MODE (BM) (Pin 9)**

Small signal output indicating deep burst mode operation. Can be coupled to control external primary-side circuits.

### PRIMARY GROUND (GD) (Pin 10)

Primary gate-drive ground. Should be capacitively decoupled to primary supply pin (BPL).

Figure 8. HiperLCS2 Primary-Side LCS726xZ, POWeDIP-20B (Top View.)

### **High-Side**

### SOURCE (S) (Pin 11)

High current Power ground return for half-bridge switch current. Also, at same potential as other small-signal primary grounds.

### **BYPASS HIGH-SIDE (BPH) (Pin 13)**

Power supply for primary high-side device. Should be capacitively decoupled to half-bridge (HB) pin. NOTE: this pin floats on the half-bridge switching voltage, can be at high-voltage with respect to primary grounds.

### HIGH-SIDE 5 V (5VH) (Pin 14)

Primary high-side small signal 5 V IC-supply pin. Should be capacitively decoupled to half-bridge (HB). NOTE: this pin floats on the half bridge switching voltage, can be at high-voltage with respect to primary grounds.

### HALF-BRIDGE (HB) (Pins 15)

High-voltage and high current connection point for low-side MOSFET DRAIN and high-side MOSFET SOURCE. The half-bridge node typically switches between primary ground and primary input bus (HD).

### NO CONNECT (NC) (Pin 16-18)

Pin not connected. Leave open.

### HD (Pin Back-Side Solder Pad) (Pin 20)

High current, high-side MOSFET Drain and connection to system high-voltage input bus.

### **BACKSIDE PAD**

This thermal pad on the back-side of the POWeDIP package, is not electrical conductive. The provides functional electrical isolation from internal switching voltages. The POWeDIP package can be directly connected to a metallic heat sink without need for additional electrical isolation.

### **UPPER and LOWER SCREW HOLES**

The upper and lower screw holes on the POWeDIP package are intended for use with M2 screws. The screws should be torqued according to recommended settings:

### **POWeDIP Mounting Instructions:**

Use thermal grease between package & heat sink.

Use M2 x 0.4 screws with M2 metal washers.

Loosely assemble package to heat sink with two screws, making sure package is centered:

- 1. Tighten first screw lightly until "snug"

- 2. Tighten second screw until "snug"

- 3. Tighten first screw again to 1.0 in-lb maximum

- Tighten second screw again to 1.0 in-lb maximum

Figure 9. POWeDIP-20B Package LCS726xZ.

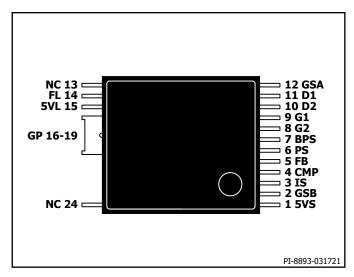

# Pin Functional Description – Safety Isolation and Secondary-Side Device LSR2000C

### SECONDARY 5 V (5VS) (Pin 1)

Connection point for an external decoupling capacitor for the secondary IC supply. Should be capacitively decoupled to secondary ground (GSB).

### **SECONDARY GROUND (GSB) (Pin 2)**

Small signal ground for secondary-side (5VS, IS, CMP, FB, PS).

### WINDING SENSE (IS) (Pin 3)

Secondary-side, small signal current input connection to an external resistor and capacitor.

### **COMPENSATION (CMP) (Pin 4)**

Secondary-side, small signal connection to external frequency compensation resistor capacitor network.

### FEEDBACK (FB) (Pin 5)

Secondary-side, small signal feedback signal to secondary control.

### PROGRAM SECONDARY (PS) (Pin 6)

Secondary-side, small signal connection for customer configuration selection components. This pin also outputs logic level fault code during fault conditions.

### SECONDARY BYPASS (BPS) (Pin 7)

Secondary-side power supply pin for secondary device.

### SR GATE2 DRIVE (G2) (Pin 8)

Secondary-side, output for driving secondary synchronous rectifier (SR) MOSFET for first output phase.

### SR GATE1 DRIVE (G1) (Pin 9)

Secondray-side, output for driving secondary synchronous rectifier (SR) MOSFET for second output phase.

### SR DRAIN2 SENSE (D2) (Pin 10)

Secondary-side, medium voltage small signal input for sensing SR DRAIN/SOURCE voltage.

### SR DRAIN1 SENSE (D1) (Pin 11)

Secondary-side, medium voltage small signal input for sensing SR DRAIN/SOURCE voltage.

### **SECONDARY GROUND (GSA) (Pin 12)**

Power ground for secondary-side (BPS, G1, G2, D1, D2).

Figure 10. HiperLCS-2 Safety Isolation and Secondary-Side LSR2000C, InSOP-24D (Top View).

### NO CONNECT (NC) (Pin 13)

No connection. Leave open.

### FLUXLINK (FL) (Pin 14)

Primary-side small signal output is the FluxLink primary output pin.

### PRIMARY 5V (5VL) (Pin 15)

Primary-side connection point for an external primary decoupling capacitor for the primary IC supply. Should be capacitively decoupled to primary ground (GP).

### PRIMARY GROUND (GP) (Pins 16-19)

Primary-side ground reference for primary BYPASS pin.

### NO CONNECT (NC) (Pin 24)

No connection. Leave open..

Figure 11. HiperLCS2–SR, Safety Isolation Package. InSOP-24D (Top View), InSOP-24D (Bottom View).

### **HiperLCS-2 Basic Operation**

The HiperLCS-2 is designed for half-bridge LLC converters, which are high-efficiency resonant ZVS, variable frequency converters.

HiperLCS-2 comes as a chipset with two devices: the power-device, and the isolation device. The power-device (LCS726x) is on the primary side of the isolation barrier and includes an LLC controller with built-in high-side and low-drivers and half-bridge power-MOSFETs. The isolation-device (LSR2000) straddles the isolation barrier to facilitate communications to the power-device (primary device). The isolation-device also includes the secondary controller and SR-driver. The HiperLCS-2 is able to operate with nominal frequencies of up to 240 kHz. It offers extremely high conversion efficiency coupled with low-component count and rugged protection features.

# HiperLCS-2 Primary-Side Power-Device Operation Start-Up Self-Bias

The HiperLCS-2 provides self-powered start-up. This means that the system provides a high-voltage bus to the HD pin and the HiperLCS-2 device will take care the rest. Self-powering is accomplished using internal high-voltage current sources. The first current source is connected between HD and the BPL pin. When voltage is applied to HD, the BPL will begin to charge any capacitance connected to this pin. There is a low pre-charge current which allows initial charging voltage to be established, and then as BPL voltage increases, this charge current is stepped to a much higher level allowing faster start-up times. This higher current capability of the BPL charging also allows the HiperLCS-2 to provide bias power to a PFC stage and allow the PFC to begin switching prior to the HiperLCS-2. Once the BPL self-charge reaches the target voltage it will enter hysteretic control. The internal current source is disabled during normal operation once an external bias (from a transformer bias winding), becomes active. The BPH pin is charged in very similar way to BPL, but the charge current from HD to BPH is lower. The BPH pin internal charge current will likewise be disabled once external bias becomes available.

In order to begin switching of an LLC converter ideally, we would prefer the half-bridge and resonant capacitor voltages to be in a known condition (preferably close to zero). The HiperLCS-2 achieves this using a high-voltage current source connected to the HB pin. This HB current source pre-conditions the resonant tank components pulling current to ground (return), prior to beginning switching. Doing this means that at initial start or restart, the HiperLCS-2 always starts with known tank conditions. The result is that the HiperLCS-2 can achieve resonant switching on the second switch edge. The pre-condition HB-current source is active prior to switching while the high-side device is below UV condition.

After all the charging conditions are complete and all undervoltage conditions are cleared, HiperLCS-2 begins switching with the high-side power-MOSFET first.

### **Start-Up Primary Soft-Start**

The HiperLCS-2 begins primary switching at a frequency approximately 1.5x the maximum of the selected switching frequency range. The switching frequency is ramped down quickly to build current in the resonant tank. Once the resonant tank achieves target current ( $I_{\text{HB}(IOVL)}$ ), the frequency is then indirectly regulated to maintain tank current at this level. The result at the system output capacitor, is equivalent to a very high-power current source. This results in a monotonic rise at the voltage on the output capacitor. The positive slew rate of the output voltage-rise will be a function of resonant tank and output capacitor values. There are two selectable thresholds,  $I_{\text{HB}(\text{OVL})}$  and  $I_{\text{HB}(\text{IOVL})}$ . The higher level  $I_{\text{HB}(\text{OVL})}$  is the default value, selected by using L pin for input voltage UV/OV functions. The lower level  $I_{\text{HB}(\text{IOVL})}$  is selected by grounding L pin and using PP pin PG

function instead. Selecting  $I_{\text{HB}(IOVL)}$  will slow the output voltage positive start-up slope and minimizes magnitude of output overshoot. Selecting  $I_{\text{HB}(IOVL)}$  is recommended for systems using an active PFC boosted input bus and requires the PFC boost to provide a powergood (PG) signal to the PP pin. Engagement of arbitrary output loads will slow the output voltage-rise but will not change the polarity of the output voltage slope. Primary control of switching continues until the output voltage reaches close to regulation at which point the secondary will take control of switching.

#### **Auto Dead Time**

The LLC-converter has a structure where positive and return voltages connect sequentially via power-MOSFET's to the mid-point or half-bridge node. The half-bridge connects to a resonant-tank network which is then series connected to typically power-return (ground) and coupled to output load. The high-side power-MOSFET and low-side power-MOSFET are driven sequentially (i.e., neither MOSFET is on at the same time). During on-time the resonant-tank delivers some energy to the output and stores the remaining energy. When the first power-MOSFET turns-off, there is a period of dead time before the second power-MOSFET turns on. During dead time some of the remaining stored energy in the resonant tank, continues to circulate current in the lumped half-bridge capacitance, causing the half-bridge voltage to slew towards the next switch. The half-bridge voltage slew continues until either the voltage is clamped by a MOSFET body-diode (ZVS), or the tank runs out of energy (non-ZVS). The goal for the LLC-converter is to always run in ZVS (zero-voltageswitching), operation. This is where the voltage across the next power-MOSFET is close to zero prior to turning on the power-MOSFET. This results in near zero capacitive (COSS) MOSFET losses. After the first power-MOSFET turns-off, the HiperLCS-2 auto-dead time function holds off second power-MOSFET until the controller detects either the end of half-bridge voltage-slew or abnormally reaches maximum dead time. Following this the second power MOSFET will turn-on. The dead time of a given LLC-converter may vary with input voltage and output load. The HiperLCS-2 will automatically adjust dead times in the range from ~90-500 ns (except for LCS7269Z where dead-time is fixed at 150 ns).

| Frequency<br>Range | Min | Nom | Max | Start | Unit |

|--------------------|-----|-----|-----|-------|------|

| 0                  | 23  | 90  | 135 | 167   | kHz  |

| 1                  | 30  | 120 | 183 | 227   | kHz  |

| 2                  | 45  | 180 | 270 | 333   | kHz  |

| 3                  | 60  | 240 | 366 | 455   | kHz  |

Table 2. Table of Primary and Secondary Frequency Ranges Selections.

Primary Device Frequency Range Selection via PP Pin Resistor

(see data table). Secondary Device Frequency Range Selection

by Part Number.

### **Primary Protection and Fault Response**

If secondary controller does not wake up within 32 ms of primary switching start, then the power device will declare fault. If hand over to secondary control does not occur within a further 32 ms after secondary wake-up, then the primary will declare a fault. As with all faults, the primary is the master of fault management. When a fault is declared (primary or secondary), the device will go into either latching (off) or non-latching fault handling.

For non-latching faults the primary device will initiate auto-restart. Auto-restart has two responses a short fault response and a long response (see Table 2).

Short fault auto-restart occurs for fault events that are detected while operating in secondary control. This auto-restart off-period is approximately 250 ms. All faults that trigger during primary control result in analog auto-restart response where the off-time is around 5 seconds.

The short-auto-restart event allows quick restart for occasional faults. The long auto-restart ensures that repetitive auto-restart maintains a very low auto-restart-attempt versus auto-restart-off-time ratio. This in turn ensures that the persistent fault does not create excess electrical nor thermal stress on the part.

The primary includes many layers of device self-protection to achieve rugged performance in the event of faults.

At power-up the device completes FMEA checks (failure-mode effect analysis) on device pins. If faults are observed the device will not start switching. Note that such an FMEA fault will not report an error code on the PP pin if it occurs prior to switching. Fault reporting messages on the PP pin are only generated for faults which occur after switching has started.

Primary half-bridge current is internally sensed during low-side MOSFET on-time. This is used for both primary start-up and also for safety current limits during secondary mode.

The primary device also includes (high-side controller) over-temperature protection. This protects against excessive power dissipation in the primary package. The device also has ambient (low-side controller) thermal protection, which prevents restart until the temperature has lowered sufficiently to allow restart. This prevents thermal temperature built up which might otherwise occur in the event of immediate restart for repeat fault conditions. Thermal fault triggers either latching or non-latching response (PP pin select).

The L pin detects input voltage for undervoltage and overvoltage protection. The input voltage is coupled via a resistor connected to L pin. The L pin is polled during burst operation to reduce system consumption. During continuous switching (non-burst) the L pin is

continuously monitored. Overvoltage and undervoltage both have hysteresis to prevent chatter. On exiting undervoltage the device goes through a restart. However, for overvoltage the device switching is blocked while the condition persists but allowed to continue when condition is removed. Note: that the L pin detects at power-up whether the pin is connected to ground or if there is a resistor between the HD pin and L pin. If the L pin is connected to ground then the PP pin power-good input function is used instead to indicate line-UV/OV conditions.

The BPL pin provides main supply voltage into the low-side driver and controller. This voltage is internally regulated to provide 5 V at 5VL pin. Note: the 5VL pin is not intended to provide power to any external devices other than the isolation device. The BPH and 5VH pins provide similar functions on the high-side driver. Both must be externally decoupled to ground with a capacitor.

The BPL, 5VL, BPH and 5VH pins are monitored for undervoltage condition. At start-up the device will not begin switching until all are above their respective UV thresholds. The pins are also monitored during normal switching and UV will trigger auto-restart. Please note that unlike faults, a UV-condition on BPL, 5VL, BPH, 5VH will force a restart but will not output a fault to the PP pin.

### **Miscellaneous Primary Functions**

At power-up, the PP pin is used to read customer configuration (resistor) settings (see Table 2), which select for the primary start-up frequency range (90, 120, 180, 240 kHz), and latching/non-latching fault handling. The PP pin may also be used to receive a power-good input signal from an external system (such as PFC controller) when the L pin is connected to ground. As mentioned previously, when PP pin (PG) function is used, the start-up current is set to the lower value of  $I_{\rm HB(IOVL)}$ . This is intended only for PFC-boost applications where the  $I_{\rm HB(IOVL)}$  slows the output voltage rise and reduces output overshoot. The same PP pin (PG) signal could be used for remote on/ off. The PP pin can also receive an external fault signal to disable device under fault or other conditions. During fault conditions the PP pin is also used to output device error codes to help with debug. The error code is output as a binary non-return-to-zero (NRZ) bit stream.

### **Primary Device PP Pin Error Fault Codes**

| Bit   | Hex<br>Code | Fault<br>Action | PP Pin Error Fault Name | Description                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | Х           | I               | 1111                    | Fixed Pre-amble.                                                                                                                                                                                                                                                                                                                                         |

| 27:20 | Х           | I               | 000 0000 0              | Fixed Pre-amble.                                                                                                                                                                                                                                                                                                                                         |

| 19    | Х           | N               | х                       |                                                                                                                                                                                                                                                                                                                                                          |

| 18:16 | X           | N               | xxx                     |                                                                                                                                                                                                                                                                                                                                                          |

| 15    | 8000h       | A/L             | HSD_OT                  | High-side MOSFET over-temperature fault. Prevents start-up switching while fault is activated and then monitored again after hand over to secondary control mode.                                                                                                                                                                                        |

| 14    | 4000h       | A/L             | AMB_OT                  | Low-side controller ambient over temperature fault. Prevents start-up switching while fault is activated and then monitored again after hand over to secondary control mode.                                                                                                                                                                             |

| 13    | 2000h       | I               | BPH_UVN                 | High-side BPH undervoltage. Prevents start-up switching while fault is activated. Not monitored in secondary control.                                                                                                                                                                                                                                    |

| 12    | 1000h       | I               | L_OV                    | Line overvoltage – activation of this fault L = OV+ causes device to stop switching and restart occurs when fault clears L = OV Fault monitored in all switching modes. Fault when active will instantaneously halt HB-switching. However if Fault is sustained for more than a few LLC periods, other faults may trigger and cause device auto-restart. |

| 11    | 800h        | A/L             | L_UV                    | Line undervoltage. Prevents start-up switching while fault is activated. Fault monitored in all switching modes.                                                                                                                                                                                                                                         |

| 10    | 400h        | L               | EXT_FAULT               | External Fault on PP pin. External circuit required to trigger this fault. Often used for secondary $\rm V_{\rm OUT}$ OV detection.                                                                                                                                                                                                                      |

| 9     | 200h        | I               | REM_OFF                 | Remote-off on PP pin (note: when L pin not used REM_OFF also generated concurrently at EXT_FAULT ). Prevents start-up switching while fault is activated.                                                                                                                                                                                                |

| 8     | Х           | N               | х                       |                                                                                                                                                                                                                                                                                                                                                          |

| 7     | 80h         | A/L             | LOST_FL_FAULT           | Lost FluxLink is monitored after start-up and hand over to secondary control mode and only when not in burst-mode. This occurs after XXXus of observing an unchanged/static FL signal while no in burst-mode. This fault can often be triggered when secondary bias is lost (BPS_UV), and secondary device stops operating.                              |

| Bit | Hex<br>Code | Fault<br>Action | PP Pin Error Fault Name | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | 40h         | A/L             | 100MS_FL_FAULT          | Lost FluxLink in burst_off (in super light load). A burst packet should occur a minimum of every 50 ms. This fault is activated if the burst packet doesn't arrive by 100 mS. This fault can often be triggered when secondary bias is lost (BPS_UV), and secondary device stops operating.                                                                                                             |

| 5   | 20h         | A/L             | START_FAULT             | Primary mode switch frequency reached FMIN. Reaching FMIN during start-up is very uncommon. This fault may indicate resonant LLC tank frequency problem or incorrect PP pin frequency-range selection.                                                                                                                                                                                                  |

| 4   | 10h         | A/L             | PCD_SS_FAULT            | Start-up problem. From start of primary switching, secondary should send wake-up command within 32 ms and hand over should occur to secondary control within 64 ms. Also during start-up frequency confirmation received signal should be received. If any of these do not occur, then error will be activated. May indicate excessive $C_{\text{OUT}}$ excessive load, or insufficient power delivery. |

| 3   | 8h          | A/L             | SEC_FAULT               | Secondary control fault is registered on the primary controller, when ALL secondary faults declared by the secondary control. For details of secondary fault see PS pin fault error code table.                                                                                                                                                                                                         |

| 2   | 4h          | A/L             | SCD_2PULSE_FAULT        | Secondary sending 2 pulse message unexpectedly in secondary control. Three messages required to trigger the fault. This fault is usually caused by grounding issues on primary ground, or magnetic coupling from the LLC transformer to the LSR2000C.                                                                                                                                                   |

| 1   | 2h          | A/L             | I_SAFETY_LIM            | Safety current limit fault in low-side MOSFET.                                                                                                                                                                                                                                                                                                                                                          |

| 0   | 1h          | A/L             | FREQ_FAULT              | Frequency confirmation failure fault. The primary control (PP selected), frequency-range, does not match frequency code received from the secondary controller. May be wrong PP pin resistor, or wrong secondary controller device.                                                                                                                                                                     |

#### Fault Action:

A/L = auto-restart or latch-off (depending on PP-selection Table 5), L = latch-off, I = information only, N = not used (ignore).

Table 3. LCS726x – Primary-Side PP Pin Error Fault Reporting.

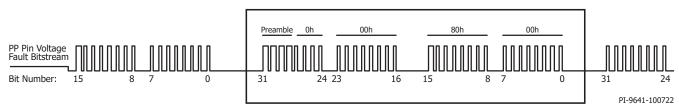

# LSR2000C - Primary PP Pin and Secondary PS Pin Error Fault Bitstream

Note1: The below PP pin error fault-code bit stream message may include multiple (concurrent) fault bits. The Fault bit stream is repetitively sent out PP pin during fault-off period. Message initially starts and bit-15 and continues to bit0. Then repeats continuously starting with MSB (Bit 31) pre-amble and ending with LSB (Bit 0). For a bit period of T, logic-1 (high for 2/3.T, low for 1/3.T), and logic-0 (high for 1/3.T, low for 2/3.T).

Below example shows primary-side PP pin bitstream during high-side over-temperature fault (HSD\_OT).

Note2: Similarly, the PS pin error fault-code bit stream message may include multiple (concurrent) fault bits. The Fault bit stream is repetitively sent out PS pin during fault-off period. Message initially starts and bit-15 and continues to bit0. Then repeats continuously starting with MSB (Bit 31) pre-amble and ending with LSB (Bit 0). For a bit period of T, logic-1 (high for 2/3.T, low for 1/3.T), and logic-0 (high for 1/3.T, low for 2/3.T).

Error Code = 0008000h : HSD\_OT (high-side over-temperature fault)

### **Secondary Device PS Pin Error Fault Codes**

| Bit   | Hex<br>Code | Fault<br>Action | PS Pin Error Fault Name | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-------------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | Х           | I               | 1111                    | Fixed Pre-amble.                                                                                                                                                                                                                                                                                                                                                                            |

| 27:24 | Х           | I               | 0000                    | Fixed Pre-amble.                                                                                                                                                                                                                                                                                                                                                                            |

| 23:18 | Х           | N               | xxxxxx                  |                                                                                                                                                                                                                                                                                                                                                                                             |

| 17:16 | X           | I               | FREQ_MODE_INFO          | Information only: read-out of the Secondary device internal Frequency Range 0-3 value. Helpful for debugging frequency confirmation faults (FREQ_FAULT), reported on the primary device.                                                                                                                                                                                                    |

| 15:14 | Х           | N               | XX                      |                                                                                                                                                                                                                                                                                                                                                                                             |

| 13    | 2000h       | P               | BPS UV FLT              | BPS undervoltage fault. This causes the secondary controller to stop operating and enter power-up state.                                                                                                                                                                                                                                                                                    |

| 12    | 1000h       | A/L             | SEC_IS_CLK_FLT          | Secondary fault triggered when slew is not detected on IS-pin signal. Often this fault will be caused when primary fault occurs and HB stops switching. Fault may indicate incorrect IS-pin components.                                                                                                                                                                                     |

| 11    | 800h        | I               | SEC_FB_OV_FLT           | FB pin overvoltage fault. Note: this fault is only active after hand over to secondary control.                                                                                                                                                                                                                                                                                             |

| 10    | 400h        | N               | Х                       |                                                                                                                                                                                                                                                                                                                                                                                             |

| 9     | 200h        | N               | х                       |                                                                                                                                                                                                                                                                                                                                                                                             |

| 8:7   | Х           | N               | XX                      |                                                                                                                                                                                                                                                                                                                                                                                             |

| 6     | 40h         | A/L             | SEC_OT_FAULT            | Secondary controller over-temperature fault. Device switching stops while fault is active.                                                                                                                                                                                                                                                                                                  |

| 5     | 20h         | I               | SEC_PHINV_FAULT         | Phase inversion fault is only active after start-up and hand over to secondary control mode. The $V_{\rm IS}$ clock is compared to the internal FL clock. If the two clocks are out of phase during 800 $\mu s$ fault timer, the fault is asserted. Cumulative switching cycles with phase inversion are required. A single switching cycle without phase inversion resets the fault timer. |

| 4:3   | Х           | N               | X                       |                                                                                                                                                                                                                                                                                                                                                                                             |

| 2     | 4h          | A/L             | VOUT_UV_FLT             | Output UV Fault become active after start-up and hand over to secondary mode. Fault is activated if FB pin remains below $V_{\text{FBBSTN}(TH)}$ for 64 ms. This fault is disabled in CC mode (PPsel6, PPsel7).                                                                                                                                                                             |

| 1     | Х           | N               | х                       |                                                                                                                                                                                                                                                                                                                                                                                             |

| 0     | 1h          | A/L             | VFB_START_FLT           | Secondary start-up fault. From end of frequency confirmation (before hand over), secondary output voltage (monitored by FB pin), if output does not reach regulation within 64 ms, the fault is activated. This fault is disabled in CC mode (PPsel6, PPsel7).                                                                                                                              |

#### Fault Action:

$A = auto-restart \ or \ latch-off \ (depending \ on \ PP-selection \ Table \ 5), \ P = power-up \ reset \ stage, \ I = information \ only, \ N = not \ used \ (ignore).$

Table 4. LSR2000C – Secondary-Side PS Pin Error Fault Reporting.

| PP Pin Selection  | Frequency Range | Fault Response |

|-------------------|-----------------|----------------|

| 0                 | 0               | Auto-on        |

| 1                 | 1               | Auto-on        |

| 2                 | 2               | Auto-on        |

| 3                 | 3               | Auto-on        |

| 4                 | 0               | Latch-off      |

| 5                 | 1               | Latch-off      |

| 6                 | 2               | Latch-off      |

| 7                 | 3               | Latch-off      |

| PP External Fault | All             | Latch-off      |

Table 5. Table of Primary-Side PP Pin Functionality Selections. See Data Table for PP Pin Selection Resistor Values.

The BM pin is used to signal that the HiperLCS-2 is operating at low load. Amongst its uses, this signal can be used to turn-on/off an inrush bypass relay. It could also be used to change the set-point of the PFC boost voltage.

The FL pin input is used to receive secondary communications, such as regulation, burst modes and faults. This input receives a digital 0-5 V signal from the FL-output of the isolation device.

# **HiperLCS-2 Secondary-Side Isolation-Device Operation**

### **Communications to Primary-Device**

As mentioned earlier the primary device will autonomously start-up and begin switching, with primary remaining in control until the output voltage reaches close to regulation. At this point the secondary will take control (primary will hand over control to secondary) and all further switching is then controlled from the secondary side controller.

The secondary-device communicates to the primary-device via the FluxLink isolated communications. Communication commands include hand over (i.e., secondary taking control), half-bridge switching, burst mode and declaration of fault condition.

The isolation-device FL-output is connected to the primary FL-input.

### **Secondary Fault Handling**

After hand over the secondary remains in control until either: a UV-event occurs (primary or secondary), or until a fault occurs (primary or secondary). Under either of these conditions UV or fault, the control reverts back to primary control. Also, under either of these conditions the primary would enter auto-restart. For auto-restart, the device has two functionalities, either latch (off-condition), or non-latching (i.e., auto-restart).

After auto-restart off-time, the primary restart is the same as for first power-up as described earlier in primary control section.

Note that the primary is the device which handles all system level fault events. Any secondary fault is reported to the primary and ultimate system level fault response comes from the primary.

### **Secondary Control**

The secondary takes control of switching as the output voltage approaches regulation. Once in secondary control, the secondary device uses 3 signals to achieve closed loop control. The FB pin signal is coupled via resistor divider from the output voltage. This FB pin voltage represents a scaled version of the output voltage. The FB pin generates an error signal with respect to an internal 3.75 V DC reference. The error signal is output via an OTA, operational transconductance (voltage input to current output) amplifier in the form of an error current signal to the CMP pin. The gain of the OTA amplifier is dependent on the magnitude of the error signal. Low gain (e.g., 1x.), is used for small errors, but once error exceeds a threshold the gain is increased to high gain (e.g. 4x.). This non-linear amplification (NLA) allows for extremely fast large-signal transient response.

The CMP pin is coupled to an external resistor capacitor compensation network (two poles one zero). This compensation network is tailored to achieve good phase-gain response. The error current signal is integrated and filtered by the compensation network. When the system is in regulation the error-current-signal should be extremely small, thus a small current causing very small variations in the CMP voltage (compensation network). Both leakage and magnetizing signals.

The IS pin senses the winding voltage from the transformer. The sense winding is coupled to the primary of the transformer (both leakage and magnetizing signals), generating a voltage whose magnitude is similar in scale to that of the main output voltage winding. The IS pin has internal clamping at 2.5 V. The sense winding voltage is AC coupled (via capacitor) and then converted to a current using a resistor into the IS pin. The magnitude of the current is low, below 35  $\mu A$ , thus causing minimal system loss.

Internally the IS pin AC-coupled current signal is compared against the CMP pin voltage. When the two cross this indicates the end of a half-cycle.

The IS pin signal contains, amongst other things, information about primary input current. This means that the overall system implements a current mode control. The control system does not directly control frequency, but instead controls half-cycle by half-cycle in time-domain. However, the frequency is an indirect function of the control loop, thus in steady state the frequency will be stable and a function of resonant tank, input voltage and output power, etc.

| PS Pin<br>Selection | Burst<br>Threshold<br>(%) ** |

|---------------------|------------------------------|

| 0                   | 15                           |

| 5                   | ~2                           |

Table 6. Table of Secondary-Side PS Pin Functionality Selections. Selected via PS Pin Resistor (see data table). \*\*Approximate Burst Percentage of Maximum Continuous System Output Power. For resistor values see LSR2000 data-table Page 38.

### **Burst Mode**

The CMP pin voltage changes inversely with respect to average primary input current. The CMP voltage is used to determine when the system should enter burst mode. The CMP burst threshold is compensated for input voltage, such that the burst-entry point should be at relatively similar power levels over the entire input voltage range.

For the HiperLCS-2 the burst mode is used for more than one reason. The first reason for burst is to maintain system efficiency. In full frequency mode the system efficiency naturally drops significantly below 10% load. So, the first goal is to enter burst mode before 10%. The regulation is achieved by switching less often but continuing to deliver the equivalent of about 10% power per switched half-cycle.

The second goal once in burst is to maintain output regulation. This is achieved using three modes of burst regulation.

The third goal once in burst is to maintain the switching frequency envelope well below the audio resonant frequency of the LLC transformer. The audio/mechanical resonance LLC-transformers is typically in the 7-12 kHz range. Thus, in burst the HiperLCS-2 intends to maintain switching frequency envelope below approximately 1 kHz. Being well below the audio resonance of the transformer means that there will be little or no noise from the transformer.

The fourth goal is to maintain ability to satisfy 0-100% load step without losing regulation. To help achieve the goals above, the HiperLCS-2 uses 3 modes of operation when in burst.

On entering burst, the highest power burst mode is called intermediate mode (IM-burst). In this mode the system is still in closed loop analog control via the CMP pin. The IM-burst works by forcing off-time at a 1.5 ms repeat period. The IM-mode off-time is terminated once the output voltage decays to a minimum value ( $V_{\text{OUT}}$ MIN). At this point switching begins again and the analog control loop closes to reach regulation. Regulation is then maintained until the off-to-off timer again reaches the 1.5 ms period. Then the next IM-mode off-time begins.

The next level down in terms of output power, is the light-load LL-mode burst. During this mode the CMP is no longer used. Instead, an internal VCMP\_BURST is used, where VCMP\_BURST corresponds to the equivalent of 10% load. The LL-mode burst switching begins when output voltage reaches  $\rm V_{out}MIN$ . The switching continues, terminating when output voltage exceeds  $\rm V_{out}MAX$ . The device enters LL-off-time until the voltage again reaches  $\rm V_{out}MIN$ . During the LL-burst switching each half-cycle delivers equal power (determined by internal VCMP\_BURST) and approximately equal to 10% load.

The lowest level of burst in terms of output power is super-light SL-burst. During this mode the switching occurs after a maximum off-time of 50 ms. The start SL-burst switching depends on the 50 ms off-time only. If the output voltage drops as far as  $V_{\text{OUT}}\text{MIN}$  then the device will move back to LL-burst. During SL-burst switch, the burst switches until either it reaches  $V_{\text{OUT}}\text{MAX}$  or reaches 60  $\mu s$  of total switching time.

With the burst modes of the HiperLCS-2 the device is able to achieve exceptional system no-load performance. Unlike other systems though it can still accommodate a full 0-100% load step without dropping out of regulation. The burst mode also intrinsically manages audio noise. The output ripple during burst is also entirely bounded by the  $\rm V_{our}MIN$  and  $\rm V_{our}MAX$  of the system. The device achieves 1% system regulation, internally the FB pin  $\rm V_{our}MAX$  and  $\rm V_{our}MIN$  thresholds are fixed at  $\pm 0.65\%$  of  $\rm V_{our}REG$ .

### SR (Synchronous Rectifier) Control

The D1 and D2 pins monitor the drain voltage of the SR MOSFET's. When D1 and D2 go below ground this indicates the potential start of SR conduction. Pins D1 and D2 require a small series resistor to prevent excessive substrate current when below ground voltage. Under certain conditions, there may be ringing on D1 and D2, and the ring may temporarily go below ground only to rise back above ground. The HiperLCS-2 therefore employs a learning engine to ignore the ringing. Therefore, when the ring-filtered value of D1 (or D2) goes below a turn-on threshold, the associated SR MOSFET is then activated. Once activated the D1 (or D2) signals then monitor the on-state Drain-Source voltage across the SR MOSFET. This gives an indication of conduction current. For an LLC-converter in discontinuous conduction mode (DCM), the rectified output current (i.e., power delivered to the secondary), will reach zero before the end of the half-cycle. In discontinuous mode (DCM) LLC operation, the detected D1 (or D2) will terminate the SR-conduction when current approaches zero. The secondary controller turns off the SR MOSFET before reverse conduction. For an LLC-converter operating in continuous conduction mode (CCM), the current will not reach zero prior to the end of the half-cycle. Therefore, to prevent reverse SR MOSFET current, the HiperLCS-2 will terminate SR-conduction prior to half-bridge switching. This can be done because the half-bridge switching signal is originated at the secondary controller. Thus, the secondary control can turn off the SR MOSFET at exactly the latest possible moment to guarantee no shoot-thru in CCM mode. This is something that allows the HiperLCS-2 to safely operate in CCM-mode with maximum SR conduction. Note: that in CCM mode, the primary and secondary rms currents are reduced vs. DCM mode. Therefore, being able to operate safely in CCM mode generally results in higher system efficiency.

### **SR Driver Voltage Clamp**

The G1 and G2 pins respectively drive the SR MOSFET's for each phase of the LLC secondary. The BPS pin voltage supplies drive current to the G1 and G2 gate-drive outputs. However, the BPS pin is able to accommodate a voltage range of up to 24 V. This would exceed the maximum gate withstand for most SR MOSFETs. Also, most SR MOSFET's are fully enhanced at voltages well below that. In order to limit the SR-MOSFET gate-charge/discharge energy, the HiperLCS-2 provides an internal voltage clamp to limit the maximum voltage output on the G1 and G2 SR-drive pins. The gate-drive voltage is internally controlled to a maximum of either 11.5 V or 6.5 V. The maximum voltage depends on the selected frequency range of the device. Frequency ranges 0,1 (90, 120 kHz), receive 11.5 V whereas higher frequency ranges 2,3 (180, 240 kHz) receive 6.5 V drive limits. Limiting the SR MOSFET drive voltage limits the gate-charge/discharge losses. Typically, higher frequency SR MOSFET's are structurally optimized to have lower  $\mathrm{V}_{\mathrm{GS}}$  turn-on thresholds and thus fully enhanced at lower voltages.

### **Layout Connections and Recommended Values**

During PC-board layout, it is important to understand the current return pin for each signal, so that correct routing paths can be implemented. The following table shows that information along with generic recommended external component values. Obviously for all designs component values may change or be optimized to suit specific conditions, however the recommended values are given as a good starting point.

| Isolation<br>Barrier | Device     | Pin          | Most<br>Sensitive | Returned to<br>Pin        | Recommended<br>Value                                                                    | Notes                                                                                                                                 |

|----------------------|------------|--------------|-------------------|---------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| <b>Primary Lo</b>    | w-Side Co  | ntrol        |                   |                           |                                                                                         |                                                                                                                                       |

| Primary              | LCS726x    | ВМ           |                   | GP                        |                                                                                         |                                                                                                                                       |

| Primary              | LCS726x    | BPL          |                   | GD                        | $1~\mu\text{F}$ / 35 V SMD right at pin. Usually also 47 $\mu\text{F}$ further from pin | The gate-drive energy comes from this pin. Large BPL pin capacitance will also be needed away from pin.                               |

| Primary              | LCS726x    | 5VL          |                   | GP                        | 1 μF / 10 V SMD<br>right at pin                                                         |                                                                                                                                       |

| Primary              | LCS726x    | FL           | **                | GP<br>(LSR2000<br>device) |                                                                                         | There is a connection from isolation device LSR2000 to LCS726x. The 5VL, GP and FL pins of both devices should be directly connected. |

| Primary              | LCS726x    | PP           |                   | GP                        | RPP at pin                                                                              | See data table for selection values.                                                                                                  |

| Primary              | LCS726x    | L            | **                | GP                        | 4 ΜΩ                                                                                    | Split resistance into at least 3 SMD resistors. Ensure that all resistors are located close to L pin.                                 |

| Primary Hi           | gh-Side Co | ntrol        |                   |                           |                                                                                         |                                                                                                                                       |

| Primary              | LCS726x    | ВРН          |                   | НВ                        | $1 \mu F / 35 V SMD right$ at pin. Usually also $10 \mu F$ further from pin             |                                                                                                                                       |

| Primary              | LCS726x    | 5VH          |                   | НВ                        | 220 nF / 10 V SMD<br>right at pin                                                       |                                                                                                                                       |

| Primary              | LCS726x    | Heat<br>Sink |                   | S                         |                                                                                         | If heat sink used ensure that it is grounded to S pin.                                                                                |

| Primary Flu          | ıxLink     |              |                   |                           |                                                                                         |                                                                                                                                       |

| Primary              | LSR2000    | 5VL          |                   | GP(LSR2000)               |                                                                                         | There is a connection from isolation device LSR2000 to LCS726x. The 5VL, GP and FL pins of both devices should be directly connected. |

| Primary              | LSR2000    | GP           |                   | GP(LCS726x)               |                                                                                         | There is a connection from isolation device LSR2000 to LCS726x. The 5VL, GP and FL pins of both devices should be directly connected. |

| Primary              | LSR2000    | FL           | **                | GP(LCS726x)               |                                                                                         | There is a connection from isolation device LSR2000 to LCS726x. The 5VL, GP and FL pins of both devices should be directly connected. |

| Isolation<br>Barrier | Device  | Pin | Most<br>Sensitive | Returned to<br>Pin | Recommended<br>Value                                                                             | Notes                                                                                                                                                                                                                       |

|----------------------|---------|-----|-------------------|--------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secondary            | Control |     |                   |                    |                                                                                                  |                                                                                                                                                                                                                             |

| Secondary            | LSR2000 | D1  | **                | GSA                | 499 ohm                                                                                          | Switch signal hence pay attention to layout/coupling.                                                                                                                                                                       |

| Secondary            | LSR2000 | D2  | **                | GSA                | 499 ohm                                                                                          | Switch signal hence pay attention to layout/coupling.                                                                                                                                                                       |

| Secondary            | LSR2000 | G1  |                   | GSA                | 4.7 ohm                                                                                          | High current gate-drive. Wider PC-board trace to limit inductance.                                                                                                                                                          |

| Secondary            | LSR2000 | G2  |                   | GSA                | 4.7 ohm                                                                                          | High current gate-drive. Wider PC-board trace to limit inductance.                                                                                                                                                          |

| Secondary            | LSR2000 | BPS |                   | GSA                | $1~\mu\text{F}$ / $35~\text{V}$ SMD right at pin. Usually also 47 $\mu\text{F}$ further from pin |                                                                                                                                                                                                                             |

| Secondary            | LSR2000 | 5VS |                   | GSB                | 10 μF / 10 V SMD<br>right at pin                                                                 | Note: this pin also has high internal current spikes, hence larger capacitor right at the pin.                                                                                                                              |

| Secondary            | LSR2000 | IS  | **                | GSB                | RIS resistor + 470 pF<br>/ 200 V capacitor                                                       | Note: the RIS resistor is typically split into two series resistors to share the voltage rating. Series resistors are placed as close as possible to the IS pin to limit external noise coupling.                           |

| Secondary            | LSR2000 | СМР |                   | GSB                | Initial values (150k + 2.2 nF) // 100 pF. All components at pin                                  | Compensation components may require modification to optimize phase-gain response.                                                                                                                                           |

| Secondary            | LSR2000 | FB  | **                | GSB                | 10 k lower resistor<br>value, at pin                                                             | The resistor divider 10 k $\Omega$ low-side resistor is used to give a good balance between no-load consumption and noise rejection. Lower values will give more noise immunity but will also increase no-load consumption. |

| Secondary            | LSR2000 | PS  |                   | GSB                | RPS at pin                                                                                       | See data table for selection values.                                                                                                                                                                                        |

Table 7. Data Sheet Body Table.

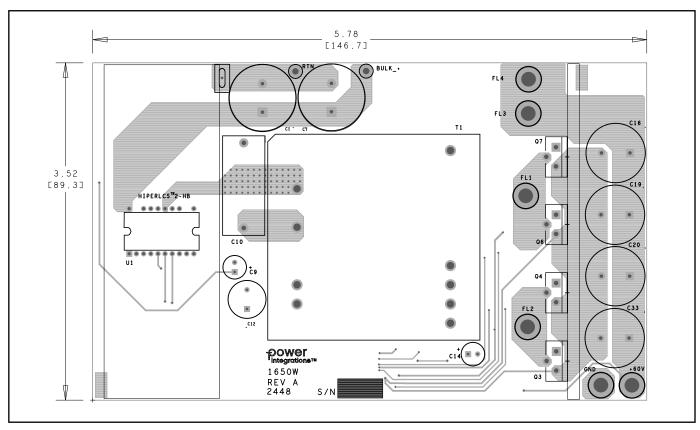

### **Basic Layout Guidelines**

The HiperLCS-2 is a high-frequency power device and requires careful attention to circuit board layout in order to achieve maximum performance. The bypass capacitors need to be positioned and laid out carefully to minimize trace lengths to the pins they serve. Surface mount (SMD) components are recommended for minimum component and PC-board stray inductance.

The HiperLCS-2 has several sensitive pins, used for sensing analog signals. Good device performance can be achieved by paying special attention to the layout at and around these pins.

On the primary-side control, both the FL pin and L pin may be sensitive to layout.

The FL pin output is essentially a digital output, so for this pin the issue is to ensure that the GP, FL and 5VL are all directly connected between the primary and isolation devices. If the grounding is not done correctly this can lead to potential noise pickup.

For the L pin this is a sensitive analog input pin. The L pin senses input voltage via a resistor (typically 4  $\mbox{M}\Omega$ ). The resistor is typically made of a series of SMD resistors. Splitting the resistance into several devices will minimize the voltage stress on each resistor. There are two different examples of how to connect the L pin to VIN. The first (incorrect) would be to place all the resistors close to VIN and then run a long PC-board trace to the L pin. This is incorrect since the node from resistor to L pin is high-impedance and a long PC-board trace would allow noise pickup injected into the L pin. The second (correct) method would be to place ALL the resistors close to the L pin and run a long PC-board trace to VIN. This method is correct since the node from resistor to VIN is very low-impedance and thus very unlikely to pick-up noise. On the secondary-side control, the FB, CMP, IS and D1/D2 pins may be sensitive to layout.

The FB pin is a high impedance voltage input pin. It is connected to  $V_{\text{OUT}}$  via a resistor divider  $(R_{\text{UPPER}},\,R_{\text{LOWER}}).\,\,V_{\text{OUT}}$  is a low-impedance node, so this may be the long PC-board connection. The node from  $R_{\text{UPPER}}$  to  $R_{\text{LOWER}}$ , is high impedance and should be placed as close and tightly coupled as possible to the FB and GSB pins. The general recommendation for  $R_{\text{LOWER}}$  is  $\sim\!20~k\Omega$ , which is a good compromise between no-load consumption and noise immunity. Further reducing  $R_{\text{LOWER}}$  would increase noise immunity but increase no-load consumption. Note that any noise injected into the FB pin could be observed as duty-cycle and/or frequency variation.

The CMP pin is a high impedance current output and voltage-input pin. The compensation network of one-resistor and two capacitors' is should be place as closely and tightly coupled as possible to the CMP and GSB pins. Any noise injected to the CMP pin could be observed as duty-cycle and/or frequency variation.

The IS pin is a current input, with a forced voltage on the pin. The IS pin signal passes from the winding-sense pin of the transformer through series capacitor CIS and resistor RIS connected to the IS pin. The transformer winding signal pin should first be connected to the CIS capacitor and then in series to the RIS resistor. The RIS resistor should be split into two SMD resistors, the last of which should be terminated right at the IS pin of the HiperLCS-2 device. The transformer should have both a winding sense signal pin and also a winding-sense small signal ground pin. The winding sense small signal transformer ground pin should be connected to the GSB pin of the HiperLCS-2. The winding sense transformer signal pin is a low-impedance node and therefore this may be the long PC-board connection. This trace however is carrying a large magnitude

(medium voltage) AC coupled signal. Thus, care needs to be taken to keep these signals away from other small signal sensitive inputs of the device.

The D1/D2 pins are both high impedance voltage inputs. The D1/D2 are connected via a low-value resistor (typically 499  $\Omega$ ), to the respective Drain of the SR MOSFET with respect to GSA pin. The SR MOSFET Drain point is a low-impedance node so may be the long PC-board connection. This trace however is carrying a large magnitude (medium voltage) AC coupled signal. Thus, care needs to be taken to keep these signals away from other small signal sensitive inputs of the device.

Transformer T1 is a source of both high di/dt signals and dv/dt noise. The high di/dt can couple magnetically (PC-board loop signal loop area coupling), to sensitive circuitry. The high dv/dt inject noise via electrostatic (stray capacitive), coupling. Electrostatic noise coupling can be reduced by grounding the transformer core, but it is not economically feasible to reduce the stray magnetic field around the transformer without drastically reducing its efficiency. Where possible, sensitive signal paths and components should be located away from the transformer to avoid noise pickup. The secondary transformer main output windings should be twisted together prior to winding. Twisting the wires together will minimize differences in secondary leakage and will enhance current balance between the windings. Also as importantly please ensure that all secondary wires are twisted together prior to termination on the transformer pin. Twisting the terminate wires will minimize wire-loop area and minimize the ability of the windings to couple stray flux to other system signals.

HiperLCS-2 primary-side power pins are the S, HB and HD pins. Unlike some designs, the HiperLCS-2 is intended for use with a single resonant capacitor. This is typically connected to primary-return (primary ground). However the device will also work if used with split resonant capacitor. Also the system can be used with  $C_{\scriptsize RES}$  clamp diodes (from ground to HB and HB to input buss). Clamp diodes limit the excursion  $C_{\text{RES}}$  voltage and in the process also impose a lower converter power limit. The HB pin is connected to the LLC transformer and the transformer to the resonant capacitor, this path length of PC-board connection should be minimized. Care should be taken to minimize return path (primary-ground) between the resonant capacitor and S pin of the HiperLCS-2 and the PC-board connection between resonant capacitor and device. The HD pin connection should also include a local decoupling capacitor from HD to primary ground (S pin potential). The goal of the local decoupling capacitor is to reduce the path length for high magnitude switched currents.

The GP ground is for small-signal circuits is used as a reference for external small-signal circuits connected to the primary device. The GP ground should NOT be connected to the bulk capacitor ground, instead GP is connected internally to HiperLCS-2 S pin ground. The S pin is connected primary-side power ground. Also the primary bias winding return and the first bias winding capacitor are also connected to power ground. The GD ground is used only to connected to the BPL decoupling capacitors, which provides gate drive power for the internal switch power MOSFETs. GD ground should NOT be connected to the bulk capacitor ground, instead it is internally connected to S pin ground.

#### Note